Description

Introduction

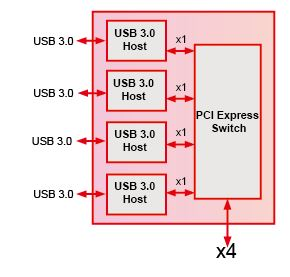

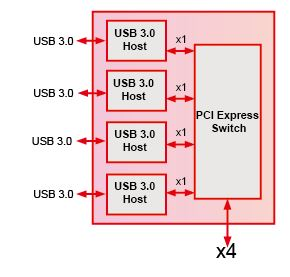

The U3X4-PCIE4XE111 is a Quad channel USB 3.0 to PCI Express x4 Gen 2 Host Adapter.

U3X4-PCIE4XE111 is designed with Two key components.

- 8-Lane, 8-Port PCI Express Switch.

- PCI Express to USB 3.0 Single Chip Host Controller (Fresco FL1100, USB IF TID 380000026).

Utilizing the standard PCI Express Switch, the 8-Lane/8-Port PCI Express Switch provides the

most efficient fan-out solution for integrating four PCI Express to USB 3.0 Single Chip Host

controllers into a small board design. Each USB 3.0 to PCI Express Single Chip Host controller

takes advantages of 5 Gbps burst rate of 4-lane PCI Express bus in both directions and is fully

compliant with PCI Express Base specification r2.0. This solution provides full PCI Express and

USB 3.0 functionality and performance.

Technical specification

Primary PCI Express

- Standards compliant

- PCI Express Base Specification r2.0 (Backwards compatible with PCIe r1.0a/1.1)

- PCI Power Management Spec r1.2

- Microsoft Vista®-compliant

- Supports Access Control Services

- Dynamic Link-width control

- Dynamic SerDes speed control

- High Performance

- Non-Blocking Internal architecture

- Full line rate on all Ports

- Cut-Thru latency: 130ns

- 2KB max payload size

- PCI Express Power Management

- Link power management states: L0, L0s, L1, L2/L3 Ready, and L3

- Device states: D0 and D3hot

- Quality of Service (QoS) support

- Two Virtual Channels (VC) per Port

- Eight Traffic Classes per Port

- Weighted Round-Robin Port & VC Arbitration

Secondary PCI Express

- Four Single (x1) PCI Express Lane

- Supports PCI Express Specification Revision 2.1 at 5GT/s

- Supports PCI Bus Power Management Interface Specification revision 1.2

- Support for Latency Tolerance Reporting (PCIe)

USB Features

- Compliant with USB 3.0 Specification Revision 1.0

- Compliant with Extensible Host Controller Interface (xHCI) Specification revision 1.0

- 4 downstream USB ports support SS/HS/FS/LS data rates (5Gbps/480Mbps/12Mbps/1.5Mbps)

- Supports UASP (USB Attached SCSI Protocol)

- Supports xHCI debug capability

- Support for Ultra High-performance isochronous applications

- Support for Latency Tolerance Tolerance Messaging (USB)

Advanced Power Saving

- Support all USB 3.0 Power States: U0, U1, U2 and U3

- Support USB 2.0 Link Power management (LPM)

- USB-IF LPM PDK Standard

- PCIe Active State Power Management (ASPM) L0s and L1

USB3 cable lock mechanism

Provides the threaded holes for the jack-screws of USB 3.0 A Plug w/Jackscrew lock Cable

USB Bus Power Input

From Power Connector 5V only. Either Big IDE 4-pin DC Power Connector or/and SATA 15pin Power Connector